光刻机一直是半导体领域的热门话题。

媒体报道,美国半导体咨询公司D2D Advisory总裁Jay Goldberg也特别指出:“英特尔代工面临的真正挑战,还在于他们的经济模式中必须要拥有更多的客户,以支持不断推进其制造流程所需的研发。必须加大外部客户需求,将收入规模增加一倍,以支持保持在摩尔定律的轨道上继续前进。”

媒体报道,台积电预计将于今年年底从ASML接收首批全球最先进的芯片制造设备——高数值孔径极紫外(High NA EUV)光刻机。这一消息标志着台积电在半导体制造领域再次迈出了重要一步。

有趣的是,台积电前期以成本为由,迟迟不肯接受High NA EUV。早些时候,台积电CEO魏哲家缺席“台积电技术研讨会2024”,而是前往荷兰埃因霍温的ASML总部洽谈设备。

如今看来,这有点像台积电的谈判游戏,也许是在与ASML争取更好的条件。

传闻魏哲家亲自与ASML谈判并达成了一项协议,通过购买新设备和出售旧型号相结合的方式,将整体价格降低了近20%。ASML同意以折扣价向台积电出售High-NA EUV设备的原因主要是因为台积电是其超级VIP客户,ASML给予了很大的让步。这一让步包括全力协助台积电进机、调校与技术支援等,以加速上线时间点。

因此,台积电的态度也发生了戏剧性的转变,由原先对新款High NA EUV光刻机价格的犹豫,转为积极寻求合作。

据悉,台积电则预计将在本季度在其位于中国台湾新竹总部附近的研发中心安装新的High NA EUV光刻机。短期内,台积电计划将High NA EUV光刻机主要用于研发,以开发客户推动创新所需的相关基础设施和模式解决方案。

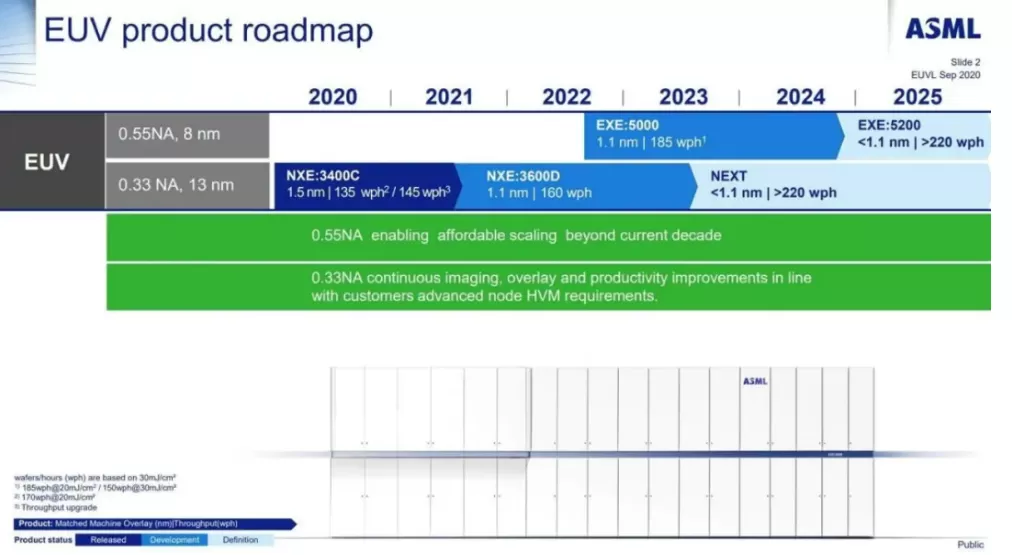

根据ASML的路线图,第一代的High-NA EUV光刻机TWINSCAN EXE:5000或许主要是被晶圆制造商用于相关实验与测试,以便公司更好地了解High-NA EUV设备的使用,获得宝贵经验。实际量产将会依赖于2024年底出货的TWINSCAN EXE:5200。

台积电即将推出的N2(2纳米级)和A16(1.6纳米级)工艺技术将完全依赖于传统的EUV设备,这些设备的光学元件具有0.33 NA。业界预计,台积电最早可能在2028年或更晚的A14(1.4纳米级)工艺技术中采用0.55 NA EUV工具,尽管目前公司尚未对此进行官方确认。

与竞争对手相比,台积电可以通过持续的生产实践积累宝贵的经验数据与优化工艺,从而难以构建起“订单驱动-技术迭代-再获订单”的良性循环体系。换言之,台积电有着极为庞大的优质客户群协助他们调试各种设备bug,这恰恰是三星和英特尔所缺少的。

台积电布局策略:无宝不落

笔者此前曾提到,从三巨头布局策略和方式来看,台积电往往被认为是一个保守技术开发者,其倾向于确保新技术的成熟和可靠性,然后再进行部署,而不是急于将新技术推向市场。

从实际的市场表现来看,台积电此举可以降低技术失败的风险,提高其芯片的产量和质量,从而确保客户的满意度。

例如,三星在2018年开始在其7nm工艺中使用EUV光刻机,然而台积电选择等待。直到EUV工具的稳定性和成熟性得到确认,以及相关问题得到解决或至少得到确定,才在2019年的N7+工艺中开始使用EUV。

此后,在FinFET向GAA工艺的过渡上,台积电依旧重操这一模式。凭借工艺领先性和生产良率上的技术优势和积累完全有实力与采用GAA技术架构的三星抗衡。

在英特尔大力押注的BSPDN背面供电技术上,台积电依旧不紧不慢,计划将在2026年底才开始大规模生产的N2P上加入。

这种谨慎的方法有助于台积电确保其制程技术的稳定性和可预测性,从而提供高质量的芯片给其客户。

但从先进封装领域来看,台积电则一改常态,积极布局率先落地,在先进制程与先进封装的组合拳下,为其带来了新的增长浪潮。

在这张弛有度的策略下,充分凸显着台积电的战略哲学和独到眼光。在其看准的蓝海赛道,台积电始终敢为人先,无论是十年前率先试产16nm FinFET制程技术超越英特尔,还是五年前部署先进封装收获如今的AI红利,台积电都精彩演绎了所谓凤凰无宝不落。

而在其保持较大优势的先进制程领域,纵然面对三星和英特尔的步步紧逼,台积电没有选择盲目激进,反而采取了先观察再跟随的策略,在做好充分的准备和规划后“亦步亦趋”,凭借自身强大的产能、良率和客户基础的基本盘优势,维持不败之地。

SK海力士发力 High NA EUV,

押宝HBM

此外,在存储领域,SK海力士的首台High NA EUV光刻机“EXE:5200”则有望2026年引入,旨在支持其先进DRAM产品的量产。这一举措进一步彰显了半导体行业对于先进制程技术的持续追求和投入。

2023年,SK海力士就曾单独组建了一个团队,专门开发High-NA EUV技术。

SK海力士作为HBM领域巨头,正不断加大对High-NA EUV技术开发的内部投入,积极扩大相关研发团队。尽管关于设备安装的具体晶圆厂位置及额外投资方向等信息尚未公开,但业界普遍预期,该技术将迅速应用于0a(个位数纳米)DRAM的规模化生产,以进一步提升产品竞争力。

写在最后

7nm以下的世界是另类冒险家的乐园,台积电,三星和英特尔的竞合关系变得愈发微妙。

根据光刻机之“瑞利公式”,光刻工艺的提升在过去几十年来一直在多维度全面出击,即不断优化曝光波长、数值孔径以及工艺因子。但目前曝光波长的缩短、数值孔径(NA)的增加都已经逼近了物理和成本综合考量的极限。

如今距离摩尔定律的极限越来越近,行业几乎走到了隧道尽头,2nm及接下来几代工艺节点将会是芯片巨头抢滩的关键。

在全球范围内,台积电、英特尔和三星等半导体巨头之间的竞争正在升温,它们竞相获得2nm以下工艺的High NA EUV设备。英特尔于2023年12月率先获得该设备,台积电于2024年第三季度紧随其后。尽管三星的订单来得晚,但实现稳定的生产可能是决定行业领先地位的关键因素。

但芯片代工的竞争,不仅仅是技术的竞争,更是客户、品牌、良率、产能等各方面的综合竞争。不知道,英特尔和三星能否在新市场的黎明期抓住重新崛起的机会。如果失败,台积电将继续独占鳌头。

未经允许不得转载:值得买 » 🈲EUV光刻机争夺战风云突变

值得买

值得买